Bối cảnh và nhu cầu thực tế

Thời gian gần đây, chủ đề thiết kế chip tại Việt Nam nhận được nhiều sự quan tâm, đặc biệt sau khi Thủ tướng Phạm Minh Chính phát động chương trình khuyến khích Việt Nam chủ động thiết kế, chế tạo và kiểm thử các dòng chip cần thiết từ nay đến năm 2027. Định hướng chiến lược mang tính quốc gia này còn là cơ hội để các trường đại học, trung tâm nghiên cứu và các ngành công nghiệp công nghệ cao đầu tư mạnh vào nguồn nhân lực, cơ sở hạ tầng và quy trình sản xuất chip.

(Trích nguồn: Báo chính phủ)

Một trong những yếu tố then chốt là đào tạo ra thế hệ kỹ sư trẻ có khả năng tiếp cận và vận hành trọn vẹn chuỗi quy trình từ ý tưởng đến sản phẩm chip hoàn chỉnh. Thực tế cho thấy, tại nhiều đơn vị, hạ tầng hiện nay vẫn thiếu và rời rạc. Nếu muốn biến một ý tưởng thiết kế thành sản phẩm khả thi, cần có một quy trình khép kín, đồng bộ từ thiết kế, mô phỏng, chế tạo, đo kiểm cho đến đánh giá hiệu suất và thử nghiệm EMC.

EMIN sẵn sàng cung cấp một bộ giải pháp toàn diện, bao gồm phần mềm, phần cứng, thiết bị đo kiểm và dịch vụ hỗ trợ kỹ thuật, giúp đơn vị triển khai đầy đủ các bước làm chip ngay tại Việt Nam.

Thiết kế chip với phần mềm Cadence và Siemens

Giai đoạn khởi đầu của quy trình là thiết kế chip tại Việt Nam trên nền tảng phần mềm chuyên dụng. Cadence và Siemens là những bộ công cụ hàng đầu thế giới, được các hãng bán dẫn, các trường đại học và trung tâm R&D tin dùng. Đây là cơ sở cho những dự án từ quy mô đào tạo tới nghiên cứu chuyên sâu.

Ở bước này, sinh viên hoặc kỹ sư có thể tiếp cận cả thiết kế analog lẫn digital, mở rộng sang các dòng chip đặc thù như RFIC và MMIC phục vụ nghiên cứu an ninh - quốc phòng, hoạt động ở dải tần rất cao từ 20 GHz tới 110 GHz, thậm chí hơn.

Quy trình thiết kế trên Cadence bao gồm xác định yêu cầu điện, nhiệt, RF và EMC, chuẩn bị bộ PDK phù hợp với node công nghệ chế tạo như 180nm hoặc 65nm. Sơ đồ nguyên lý được vẽ bằng Virtuoso Schematic Editor, sau đó mô phỏng hoạt động điện ở các chế độ DC, AC, Transient, Noise bằng bộ mô phỏng Spectre. Khi đã có sơ đồ hoàn chỉnh, kỹ sư tiến hành thiết kế layout, tuân thủ kiểm tra DRC và LVS để đảm bảo tính chính xác. Các parasitic được trích xuất bằng Cadence QRC hoặc Assura để tính toán ảnh hưởng ký sinh lên mạch trước khi gửi đi chế tạo.

Mô phỏng trường điện từ và tối ưu hệ thống với ANSYS

Khi layout đã hoàn thành, cần đánh giá tác động của trường điện từ và các hiệu ứng ký sinh lên toàn bộ hệ thống. Đây là bước quan trọng trong giải pháp Cadence/ANSYS, giúp dự đoán khả năng hoạt động thực tế của chip khi tích hợp vào PCB hoặc sản phẩm hoàn chỉnh.

Từ Cadence, kỹ sư xuất dữ liệu layout hoặc mô hình 3D ở định dạng GDSII, OASIS hoặc S-parameter để nhập vào các công cụ của ANSYS. HFSS dùng để phân tích RF/EM, S-parameters, bức xạ và khả năng tương thích điện từ. SIwave phân tích integrity của tín hiệu tốc độ cao và nguồn cung cấp. Q3D Extractor tính toán và giảm các tham số điện dung, điện cảm ký sinh. Icepak mô phỏng và tối ưu tản nhiệt.

Những kết quả này được đưa ngược về Cadence để thực hiện mô phỏng hậu-layout, cho phép điều chỉnh layout hoặc schematic nếu cần, trước khi tape-out gửi tới foundry. Việc tuân thủ các tiêu chuẩn quốc tế như MIL-STD hoặc IEC 61967 ở bước này giúp đảm bảo sản phẩm có độ tin cậy cao.

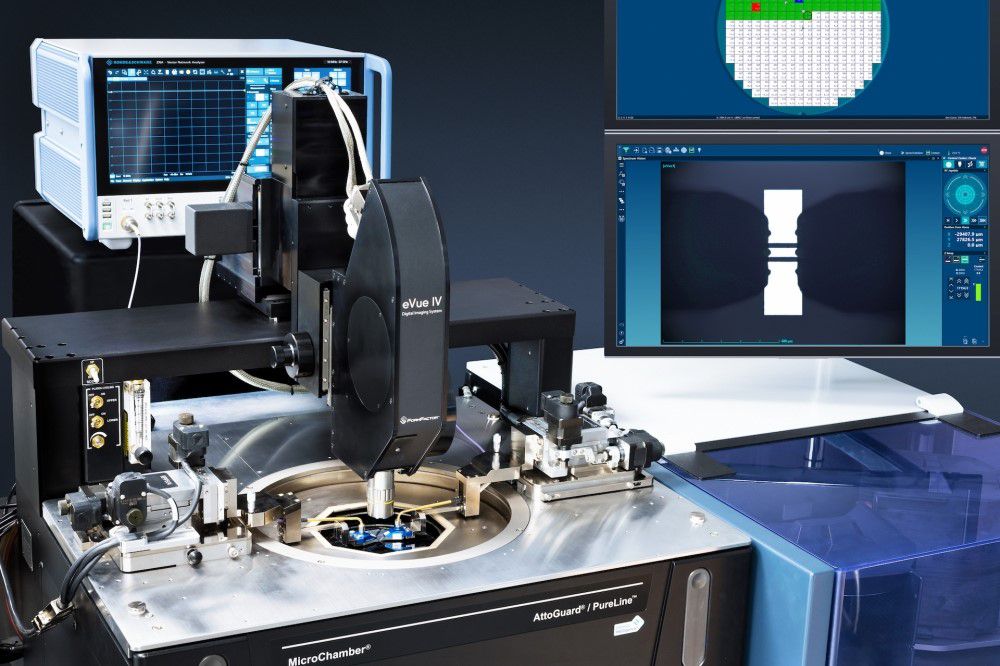

Đo kiểm chip trực tiếp trên wafer với probe station

Khi chip được chế tạo và trả về dưới dạng bare die hoặc trên wafer, đo kiểm chip với probe station là bước không thể bỏ qua để xác minh thông số và hiệu suất.

Hệ thống đo kiểm wafer thường gồm probe station với bàn dịch chuyển X-Y-Z và hệ thống chân không, microscope để quan sát và căn chỉnh chính xác, microprobe dạng GSG, GS hoặc coaxial phù hợp dải tần đo. Hệ thống đo đi kèm các dòng máy phân tích mạng vector (VNA), máy phân tích phổ (spectrum analyzer), máy phát tín hiệu (signal generator) từ các hãng mà EMIN phân phối như Rohde & Schwarz, Anritsu…, đảm bảo đáp ứng dải tần yêu cầu.

Cáp RF và adaptor chuẩn SMA, K, 2.4 mm hoặc 1.85 mm đảm bảo truyền tín hiệu chính xác. Bộ calibration kit tương ứng với loại probe, kèm calibration substrate có pad chuẩn Open, Short, Load, Thru, giúp hiệu chuẩn SOLT, TRL hoặc LRRM ngay tại đầu probe.

Quy trình đo bao gồm bật thiết bị, khởi động hệ thống, lắp và kết nối probe, hiệu chuẩn, đặt mẫu chip lên chuck (có thể dùng chuck nhiệt), căn chỉnh pad đo, hạ probe tiếp xúc vừa đủ để không làm xước pad, sau đó quét tần số, điều chỉnh điện áp bias hoặc nhiệt độ theo yêu cầu. Dữ liệu đo được lưu lại và phân tích bằng R&S, Keysight ADS hoặc MATLAB để so sánh với kết quả mô phỏng.

Đánh giá chip trên PCB

Khi chip đã đạt yêu cầu trên wafer, bước tiếp theo là gắn chip lên PCB để kiểm tra trong môi trường tích hợp thực tế. Lúc này, giải pháp Cadence - ANSYS tiếp tục được sử dụng để mô phỏng hoạt động điện từ của chip khi kết hợp với các linh kiện khác, đánh giá ảnh hưởng của layout PCB tới tín hiệu và nguồn, khả năng tản nhiệt, cũng như các hiện tượng bức xạ. Kết quả này giúp kỹ sư tinh chỉnh thiết kế trước khi sản xuất hàng loạt.

Kiểm tra EMC cho chip và hệ thống

Với những dự án tại các trường trọng điểm, chip và hệ thống sẽ được kiểm tra EMC để đánh giá khả năng tương thích điện từ. Phòng EMC thực hiện các phép đo theo tiêu chuẩn IEC, CISPR hoặc MIL-STD, bao gồm đo phát xạ nhiễu dẫn, nhiễu bức xạ và đo khả năng miễn nhiễm với nhiễu.

Kết quả đo EMC sẽ được so sánh với mô phỏng từ giải pháp Cadence/ANSYS, giúp phát hiện và khắc phục sai lệch trước khi đưa sản phẩm ra thị trường.

Giải pháp trọn gói từ EMIN

EMIN cung cấp đầy đủ phần mềm, phần cứng và hỗ trợ kỹ thuật cho toàn bộ quy trình, từ thiết kế chip tại Việt Nam, mô phỏng bằng giải pháp Cadence/ANSYS, cho đến đo kiểm chip với probe station và kiểm tra EMC.

Kết luận

Quy trình làm chip đòi hỏi sự phối hợp của nhiều công cụ và thiết bị chuyên dụng. Sở hữu một giải pháp đồng bộ sẽ giúp rút ngắn thời gian phát triển, nâng cao độ chính xác và khả năng thương mại hóa sản phẩm.