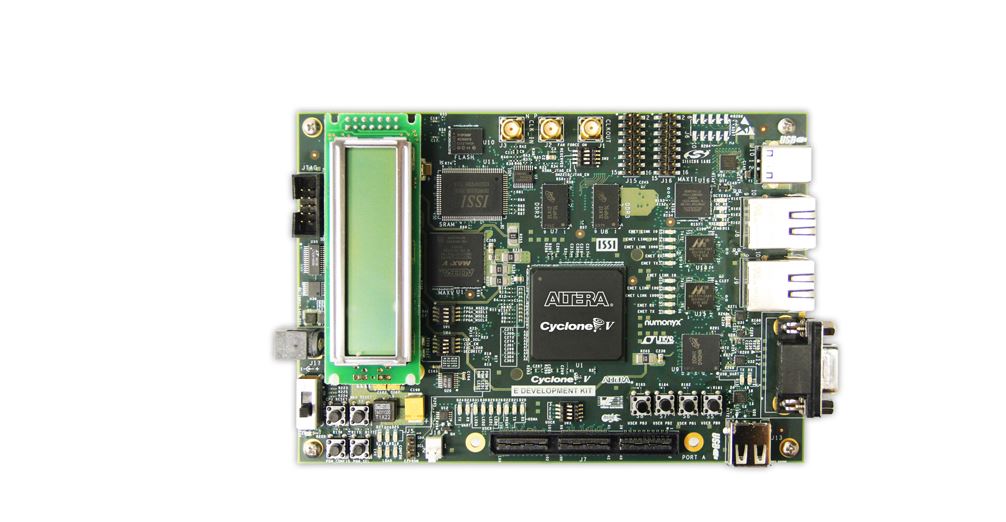

Terasic Altera Cyclone VE FPGA开发板

制造商: Terasic Model: Cyclone V E - 联系

Featured devices:

Cyclone V E FPGA - 5CEFA7F31C7NES

MAX V CPLD - 5M2210ZF256I5N (system controller)

MAX II CPLD - EPM240M100I5N (embedded USB Blaster II)

Configuration:

On-board USB-BlasterTM II cable (USB, PHY, Max® V CPLD)

JTAG direct via JTAG header

Memory devices

DDR3 x32 at 300 MHz (soft memory controller)

LPDDR2 x16 (soft memory controller)

Flash (512 Mb)

SSRAM (18 Mb)

EEPROM (64 Kb)

General user input/output

User control

Four pushbuttons

Five LEDs

Four DIP switches

2x Resets (CPU reset, Dev Clear)

LCD: Character LCD (16x2)

Components and interfaces

RJ45 for Ethernet

UART interface

Quartus® II design software information

Quartus II Web Edition Software

The Cyclone® V E Development Kit offers a comprehensive general purpose development platform for many markets and applications, including: Industrial Networking, Military, and Medical applications. The kit features an the Altera® Cyclone V device and a multitude of on board resources including: multiple banks of DDR3 and LPDDR2 memory, LCD character display, LEDs, user switches, USB and RJ-45 connectors. The Cyclone V E Development Kit gives industrial equipment designers greater flexibility in implementing real-time Ethernet communications with Industrial Ethernet intellectual property (IP) cores.

- 质量承诺

- 正品保修

- 送货到家

- 交易简单化