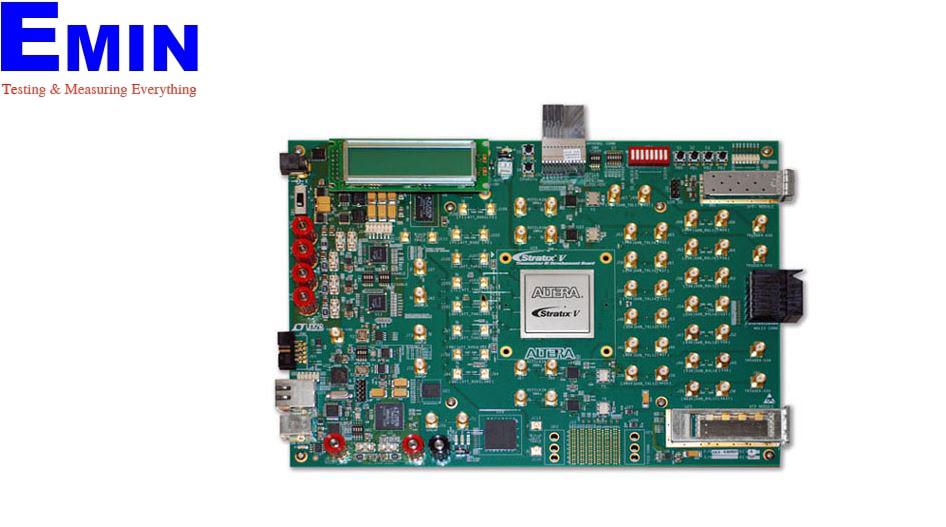

Terasic Altera Transceiver Signal Integrity Development Kit, Stratix V GT Edition

Manufacturer: Terasic Model: Stratix V GT Edition - Request a Quotation

- Request a Quotation

- Contact

See more: Equipment Calibration-Inspection & Repair Service

Call for the best price

Hanoi city: (024) 35.381.269

Danang city: (023) 63.747.711

Bac Ninh city: (0222) 730.39.68

Hai Phong city: (0225) 730.03.89

HCM city: (028) 38.119.636

Dong Nai: 0345.689.536

Featured device

5SGTMC7K3F40C2N

Configuration status and set-up elements

JTAG

On-board USB-BlasterTM

Fast passive parallel (FPP) configuration via MAX® II device and flash memory

Two configuration file storage

Temperature measurement circuitry (die and ambient temperature)

Clocks

50 MHz, 125 MHz, programmable oscillators (preset values: 624 MHz, 644.5 MHz, 706.25 MHz, and 875 MHz)

SMA connectors for supplying an external differential clock to transceiver reference clock

SMA connectors for supplying an external differential clock to the FPGA fabric

SMA connectors to output a differential clock from the FPGA's phase-locked loop (PLL) output pin

General user input/output

10-/100-/1000-Mbps Ethernet PHY (RGMII) with RJ-45 (copper) connector

16x2 character LCD

One 8-postion dipswitch

Eight user LEDs

Four user pushbuttons

Memory devices

128-megabyte (MB) sync flash memory (primarily to store FPGA configurations)

High speed serial interfaces

Four full-duplex GTB (28.05 Gbps) transceiver channels routed to MMPX connectors

Seven full-duplex GXB (12.5 Gbps) transceiver channels routed to SMA connectors

Short trace routed on a micro-strip

Six strip-line channels from the with all the trace lengths are matched across channels

21 full-duplex GXB transceiver channels routed to backplane connector

Seven channels to Molex® Impact® connector

Seven channels to Amphenol® XCede®

Seven channels to footprint of Tyco Strada® Whisper® (connector is not populated)

Power

Laptop DC input

Voltage margining

The Altera® Stratix® V GT Transceiver Signal Integrity (SI) Development Kit provides a platform for electrical compliance testing and interoperability analysis. The accessibility to multiple channels allows for real-world analysis as implemented in the system with transceiver channels available through SMA and popular backplane connectors. You can use this development kit to perform the following tasks:

- Evaluate transceiver link performance up to 28 Gbps

- Generate and check pseudo-random binary sequence (PRBS) patterns via a simple to use GUI (does not require the Quartus® II software)

- Access advanced equalization to fine tune link settings for optimal bit error ratio (BER)

- Perform jitter analysis

- Verify physical media attachment (PMA) interoperability with Stratix V GT FPGAs for targeted protocols, such as CEI-25/28G, CEI-11G, PCI Express® (PCIe®) Gen 3.0, 10GBASE-KR, 10 Gigabit Ethernet, XAUI, CEI-6G, Serial RapidIO® , HD-SDI, and others

- Use the built-in high speed backplane connectors to evaluate custom backplane performance and evaluate link BER

- Quality Engagement

- Easy change and return

- Delivery Avaliable

- Favorable payment